カスタムロジックでMCUの性能を爆発的に向上

(出典:Archara / stock.adobe.com; AIで生成)

電子システムの設計には常に妥協が伴いますが、現代の設計では、より高い性能、追加機能、より小さなフォームファクター、より少ない電力使用、より低いコスト、またはこれらの目標の組み合わせが求められるため、エンジニアにとってかつてないほど難しい課題となっています。

これらの課題に取り組む方法のひとつが、カスタマイズ可能なロジックです。カスタムロジックは、マイクロコントローラ(MCU)内部に小型のフィールド・プログラマブル・ゲートアレイ(FPGA)を搭載しているようなもので、ロジック機能を処理するためにソフトウェアや外部ハードウェアだけに頼るのではなく、設計者はマイクロコントローラ内部にカスタムのハードウェアベースの機能を組み込むことができます。これにより、デザイナーは外部コンポーネントに大きく依存することなく、処理速度を向上させ、電力効率を最適化することができます。 このブログでは、MCUのカスタムロジックが提供する利点のいくつかを探り、Microchip Technologyの包括的なソリューションを検証します。

パフォーマンスの向上

MCUの消費電力を最小限に抑えることは、システム全体の消費電力に大きく影響するため、非常に重要です。MCUはシステムの頭脳であり、設計上の制約を満たすためには適切なMCUを選択することが極めて重要です。必要なパフォーマンスを提供し、アップグレードの余地があるべきです。さらに、一般的な機能のための統合周辺機器は、設計プロセスを簡素化し、部品点数を削減し、基板スペースを節約します。

Microchip Technology社は、主要システム周辺機器をパッケージに組み込むことでMCUを革新し、中央処理装置(CPU)から独立して機能できるようにしました。これらのコア独立周辺機器(CIP)は、CPUの監視なしに特定のタスクを処理し、CPUがスリープモードを維持したり、他のタスクに集中できるようにします。各 CIP は、安全性の監視や波形の調整など、特定の機能向けに設計されており、用途に合わせてカスタマイズすることも可能です。

CIPは、CPUベースの実装よりも応答時間が速く、CPU時間とメモリ競合が削減されるなどの利点があります。さらに、設計者は電力やメモリ使用量に合わせて設計を最適化することができます。

新しいレベルの柔軟性

CIPは一般的なタスク向けの事前定義された機能を提供しますが、アプリケーションによってはより柔軟性が必要な場合もあります。 このような場合に利用されるのが、カスタムロジックブロック(CLB)です。 特定の機能向けに設計されたCIPとは異なり、CLBはエンジニアがニーズに合わせて構成できる完全にカスタマイズ可能なロジックを提供します。

Microchip Technology社はCIPの理念をさらに推し進め、PIC16F131xxマイクロコントローラファミリにCLBを導入しました。CLBはCIPと同様にコアとは独立して動作しますが、定義された機能はありません。その再プログラム可能な論理設計は、多くのアプリケーションに対応できるようカスタマイズが可能です。CLBは、省電力、パフォーマンスの向上、高度に統合された設計など、CIPのすべての利点をもたらし、設計者は完全にカスタマイズされたアプリケーションを実装することができます。

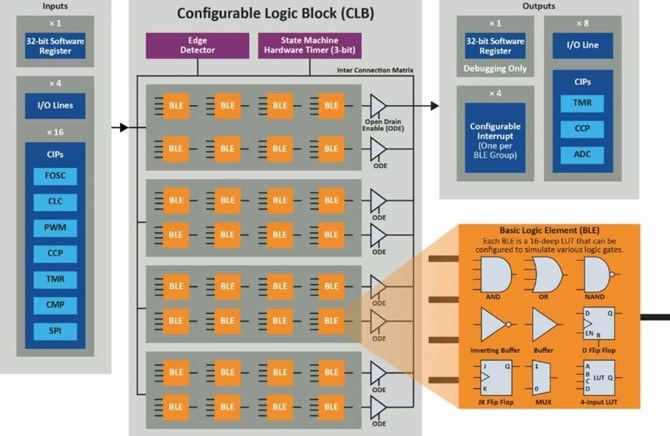

CLB回路には、4つのブロックに配置された32個の基本論理素子(BLE)があります。各BLEは、AND/OR/NAND/NORゲート、バッファ/インバーティングバッファ、Dフリップフロップ、J-Kフリップフロップ、またはマルチプレクサをシミュレートするように構成できます(図1)。

図1:CLBアーキテクチャは、BLE、入出力接続性、エッジ検出やステートマシンタイマなどのハードウェア機能を備え、組み込みシステムの柔軟性を高める。(出典:Microchip Technology)

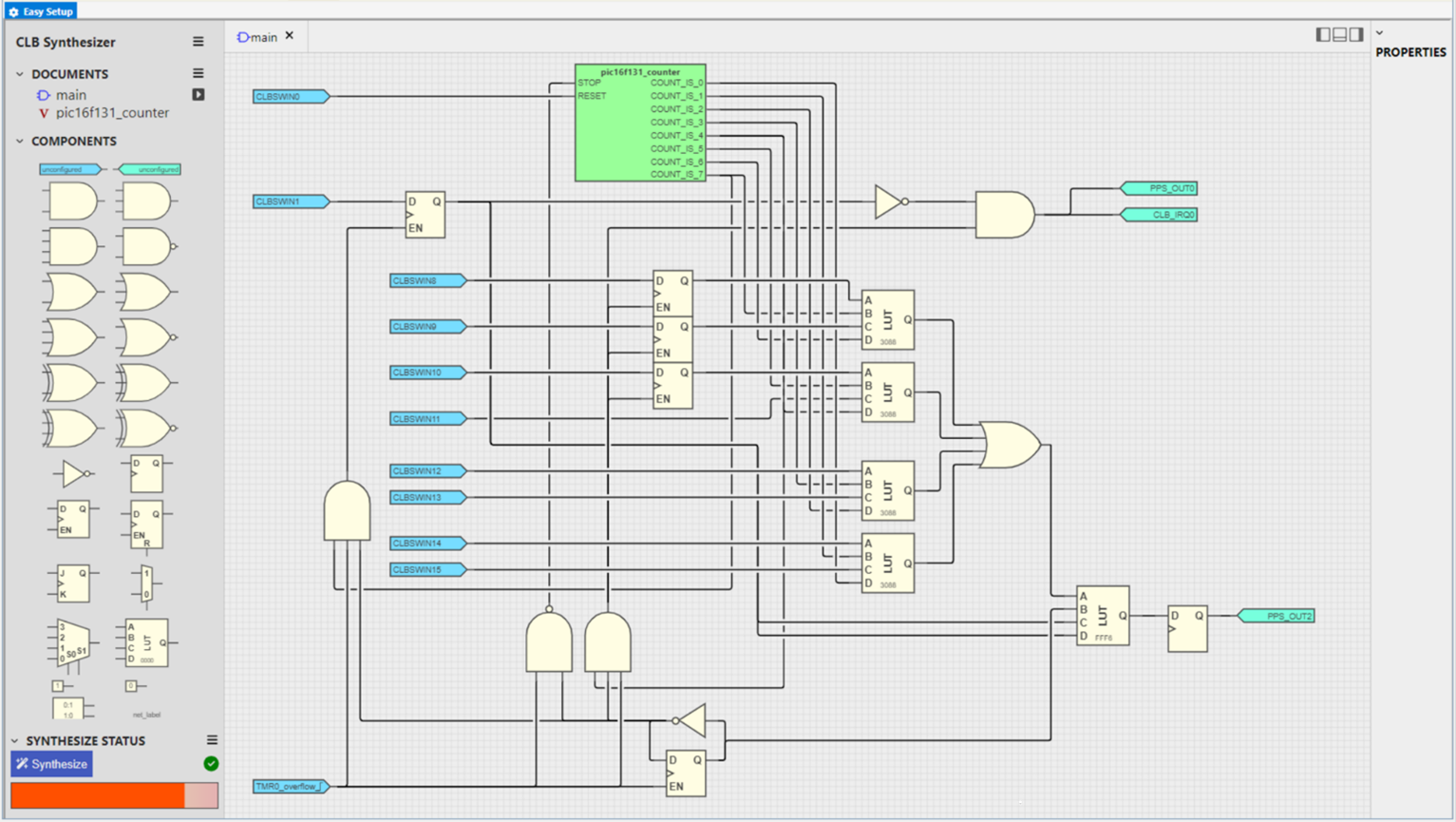

CLBは、迅速な変更やトライステートロジックのための動的構成もサポートしています。各BLEは、他のBLEブロック、レジスタ、カウンター、さらには外部ペリフェラル、I/O、オシレータ、さらには他のCIPにも内部的に接続することができます。さらに、各BLEには4入力ルックアップテーブル(LUT)、組み合わせロジック、およびフリップフロップが搭載されています。Microchip社のMPLAB®コ-ドコンフィギュレータ(MCC)のGUIベースのCLBグラフィカルシンセサイザは、BLEブロックをカスタマイズでき、コーディング不要で設計を構築し、合成することができます。

CLBの実践的な例

グルーロジックは、CLBテクノロジーの利点を最もよく示すものです。現在では、異なる回路領域を論理ゲートや電圧レベル変換でつなぐといったグルー機能に個別部品やプログラマブル・ロジックが使用されています。CLBテクノロジは、デザインに部品を追加することなく、同じタスクを迅速かつ容易に実行できます。CLBのプログラマビリティにより、必要に応じてグルーロジックを再構成することも可能です。

CLBテクノロジーに最適な分野のもう一つは、エンコーディングとデコーディングです。これは繰り返し行われる作業であり、プログラマブルロジックに最適です。例えば、PoDL(Power over Data Line)通信は、電源とデータに単一のワイヤペアのみが必要なシンプルな構造であるため、普及が進んでいます。PoDLではマンチェスタ符号化が使用されており、両端間のデータの同期とエラー検出を行うことでデータの完全性を確保しています(図2)。 ディスクリートエンコーダは大型の受動素子を必要とし、ソリューションのサイズとコストの両方が増加します。 CLBテクノロジーはエンコーディングプロセスを高速化し、より高速なデータレートを可能にします。

図2:CLBベースのマンチェスタ符号器は、特定のビットレートに簡単にカスタマイズできる。(出典:Microchip Technology)

CLBテクノロジーは、故障検出において従来のテクノロジーよりも優れた利点を提供することができます。多くの回路では、リアルタイムで一般的な故障をチェックし、故障が検出された場合は回路を安全な状態にするために、故障検出が必要です。これらのチェックは通常、サーキットの動作性能に影響を与えることなく、非常に迅速に行う必要があります。つまり、より迅速なレスポンスとより予測可能なタイミングを持つハードウェアが望ましいソリューションであるということです。エラー検出にMCUベースのソフトウェアを使用するのは困難です。なぜなら、エラー状態には一定のタイミングがなく、ソフトウェアのエッジケースでは安全な状態を遅延させるエラーが発生する可能性があるからです。この役割には、ディスクリートプログラマブルロジックデバイスがよく使用されますが、これは高価であり、統合には追加の設計時間が必要です。CLBテクノロジは、シングルチップで同等の、またはより優れた性能を実現できます。

タイミング制御と電源シーケンスも、複雑な組み込みシステムでは重要です。電源に敏感な設計では、安定性を確保し、コンポーネントの損傷を防ぐために、電源投入と電源切断のイベントの正確な順序がしばしば必要になります。通常、このためには外部電源シーケンスICまたはソフトウェア制御シーケンスが必要です。これにより、プロセスが複雑化し、遅延が生じる可能性があります。CLBでは、電源シーケンスロジックをハードウェアに直接組み込むことができるため、設計者は電源レールが正しい順序で確実に起動および停止するようにし、遅延を最小限に抑えることができます。

最後に、CLBテクノロジーは冗長性を目的としてシステムの一部分を複製するために使用でき、単一障害点を排除することができます。例えば、MCUで実行される単純な機能にはCLBベースのバックアップを設け、MCU機能にソフトウェアエラーが発生した場合でも、このロジックベースのバックアップは機能します。

結論

現在の組み込みシステムは、より複雑かつ電力効率が向上しており、設計者は処理能力だけでなく、より多くの機能をもたらすマイクロコントローラを必要としています。 設計者は柔軟性を求めています。 Microchip Technology社のCLBは、FPGAのような構成をマイクロコントローラにもたらし、外部コンポーネントを削減し、性能を向上させ、電力効率を最適化します。

現在の組み込みシステムは、より複雑かつ電力効率が向上しており、設計者は処理能力だけでなく、より多くの機能をもたらすマイクロコントローラを必要としています。 設計者は柔軟性を求めています。 Microchip Technology社のCLBは、FPGAのような構成をマイクロコントローラにもたらし、外部コンポーネントを削減し、性能を向上させ、電力効率を最適化します。